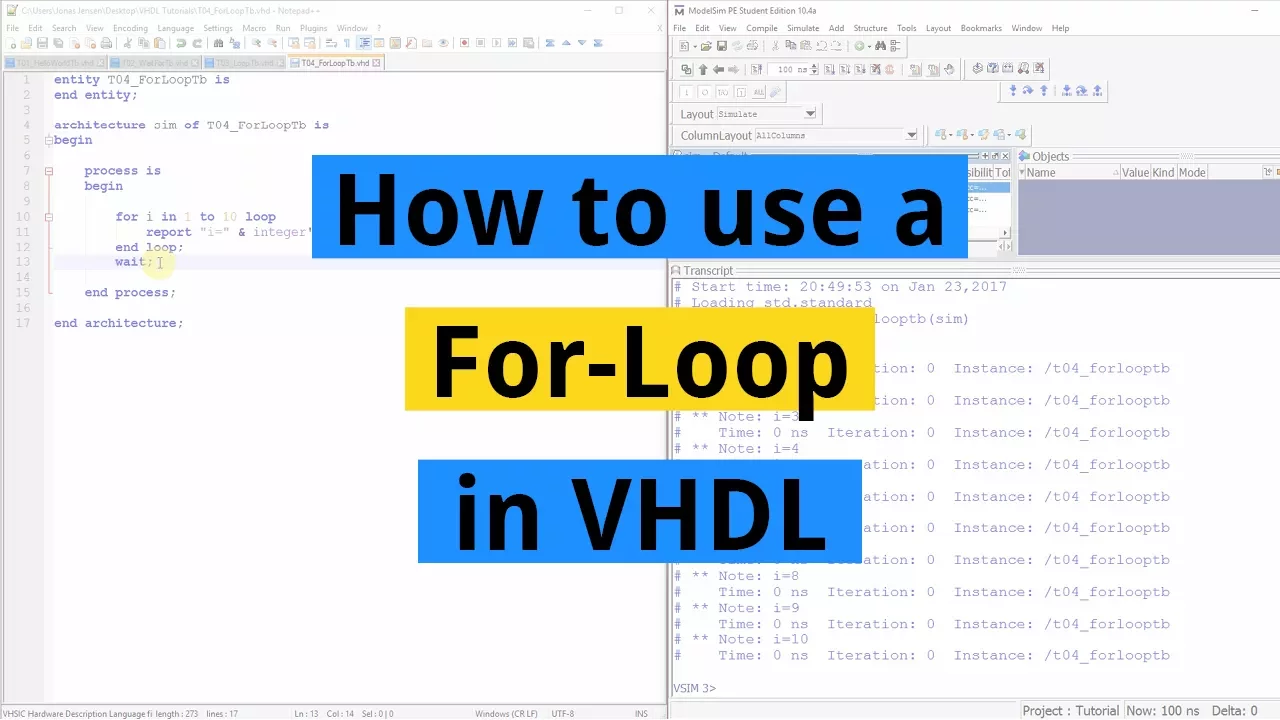

How to use a For-Loop in VHDL

Learning to Use For Loops in VHDL

In this section, Jonas introduces the concept of using for loops in VHDL to iterate a fixed number of times.

Introducing For Loops

- Jonas demonstrates how to use the for loop by iterating through a range of numbers from 1 to 10.

- The for loop iterates 10 times, with each iteration represented by the constant 'I'.

- Within the loop, Jonas adds a report statement to print out the value of 'I' during each iteration.

Converting Integer to String

- To print an integer as a string in VHDL, Jonas explains using the attribute 'integer'image.

- After completing the code, he compiles it in ModelSim and initiates a simulation successfully.

Simulation and Conclusion

- Starting the simulation in ModelSim, Jonas showcases how the program prints values from 1 to 10 before hitting the wait statement.