DDCA Ch4 - Part 6: SystemVerilog Assignments

Detailed Explanation of Blocking and Non-Blocking Assignments

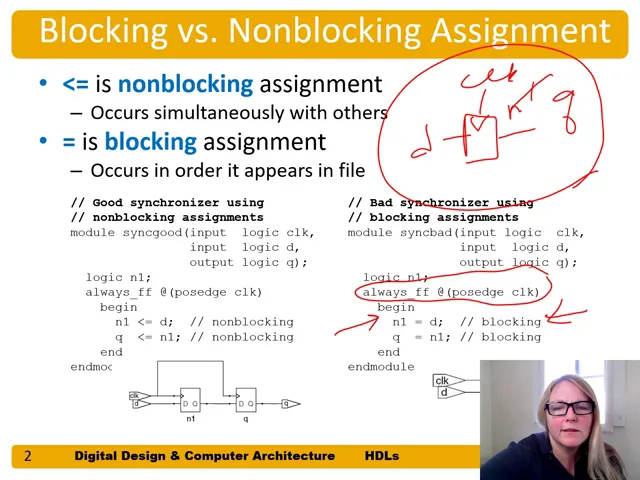

The discussion delves into the distinctions between blocking and non-blocking assignments in signal processing, emphasizing their impact on simultaneous versus sequential signal assignment.

Blocking vs. Non-Blocking Assignments

- Blocking assignment uses the equals sign (=) and executes statements sequentially, following the order in the file.

- Non-blocking assignment employs the gets operator (<=), enabling simultaneous signal assignments.

- In a blocking assignment scenario, signals are assigned one after another in sequence, affecting the order of execution.

- Non-blocking assignments allow for parallel signal assignments, enhancing efficiency but requiring careful consideration to avoid unintended consequences.

- Understanding these assignment types is crucial in designing synchronous sequential logic circuits effectively.

Signal Assignment Techniques in Hardware Description Languages

This segment explores various methods of assigning signals within hardware description languages, highlighting nuances between continuous and blocking assignments.

Signal Assignment Methods

- Synchronous sequential logic often utilizes always_ff at pos edge clock with non-blocking assignments for stable circuit operation.

- Continuous assignment statements like assign y = a and b ensure constant updates based on changing input values, synthesizing into logical gates for implementation.

- Employing blocking assignments within case or if else statements can streamline complex combinational logic design by enforcing sequential execution flow.