Архитектура ЭВМ Лекция 11: Организация ввода вывода. Интерфейсы передачи данных.

Introduction to Input-Output Operations

The discussion delves into the concept of input-output operations in computing, emphasizing the necessity for computers to interact with external devices for program execution.

Understanding Input-Output Devices

- Input-output devices like keyboards, monitors, printers, and hard drives are essential for computer interaction with the external world.

Supporting Output in Computer Architecture

- Two key tools enable communication with the external world: executing instructions through the processor and interacting with memory to read and write data.

Mechanism of Interrupts for Device Interaction

- Interrupts serve as a mechanism for device interaction, allowing devices to signal the processor when attention is required.

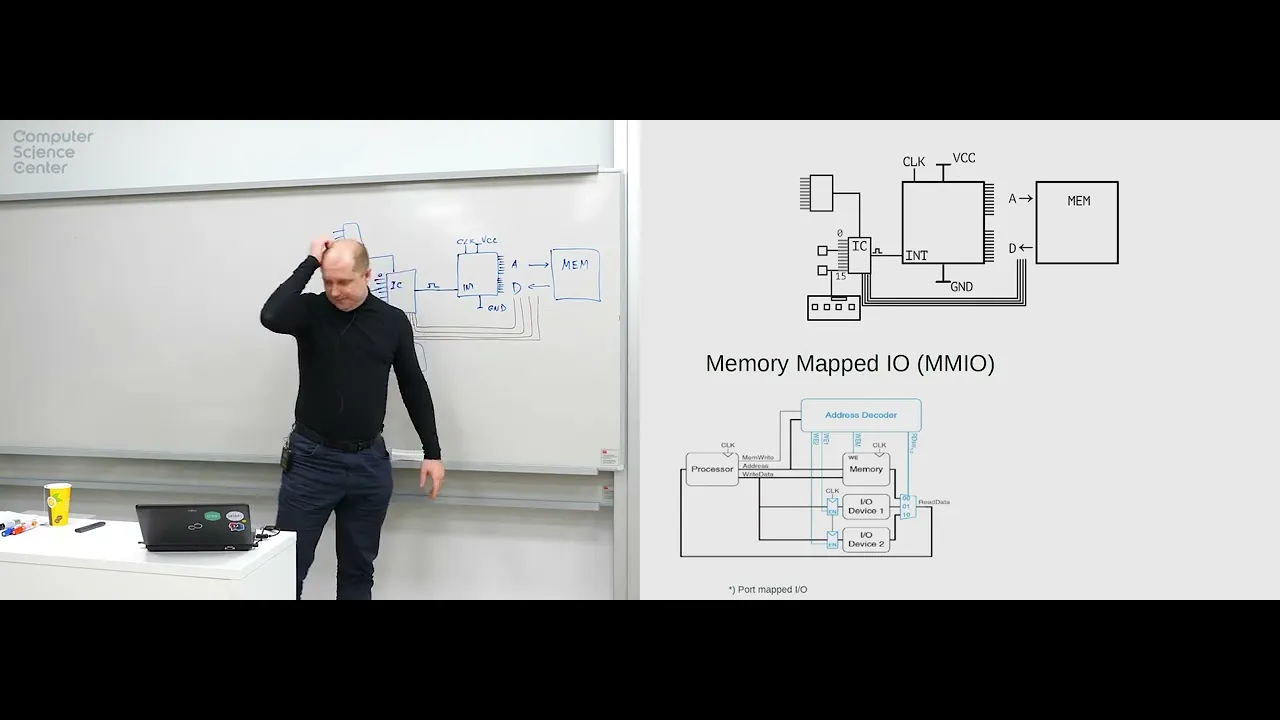

Physical Representation of Processor Interfaces

The segment explores the physical aspects of processor interfaces and their role in facilitating communication with memory and devices.

Processor Pin Configuration

- Processors consist of multiple pins serving various functions such as power supply (VCC), ground connection (GND), address bus for memory interaction, and data bus.

Memory Interface via Address and Data Buses

- Processors utilize address buses to communicate memory locations and data buses for actual data transfer, highlighting the distinct interface between processors and memory units.

Utilizing Interrupts for Device Signaling

The discussion elaborates on interrupts as a fundamental tool for connecting physical devices to processors.

Role of Interrupt Signals

- Interrupt signals act as a basic yet effective means of linking physical devices to processors, enabling event notifications that trigger appropriate processing actions.

Challenges in Synchronization

- Synchronization poses a challenge in managing multiple device connections efficiently due to synchronous operation requirements across all components.

Chipset Functionality in Device Management

Chipsets play a crucial role in coordinating various devices within a computing system.

Chipset Components

- Chipsets encompass multiple microchips working collectively to manage diverse hardware components effectively within a computer system.

Integrating Interrupt Controllers

New Section

In this section, the speaker discusses issues related to interrupt handling and the need for efficient interrupt processing.

Understanding Interrupt Handling

- The speaker emphasizes the importance of considering the type of interrupt being dealt with and highlights the necessity for a clear understanding of interrupt processing.

- It is explained that when a keyboard generates an interrupt, it should not require individual interrupts for each key press. Instead, an interrupt handler should be called to manage keyboard interrupts efficiently.

- The discussion moves to how interrupt controllers can also act as data buses, adding complexity to identifying the source of interrupts.

- The controller's ability to write data on the data bus before triggering an interrupt is highlighted as a crucial step in efficient interrupt handling.

Efficient Interrupt Processing

- Once a specific device generating an interrupt is identified, understanding its nature allows for effective resolution of the issue at hand.

- The significance of instructions like "set-inter" and "clear-interact flag" in x86 architecture is explained in relation to processor behavior during interrupts.

New Section

This section delves into further complexities surrounding device communication and introduces additional concepts related to handling interruptions effectively.

Device Communication Challenges

- Devices often struggle to synchronize with processors regarding when they can or cannot generate interrupts, posing challenges in communication protocols.

- Introducing two new pins named "inter" and "int-a," which can be connected to an interrupt handler, streamlining communication processes between devices and processors.

- A detailed explanation is provided on how these pins facilitate device interaction with processors by signaling readiness for interruption after specific conditions are met.

Utilization of Interrupt Controllers

- Interrupt controllers play a vital role in managing interactions between devices and processors, ensuring seamless operation through coordinated signaling mechanisms.

New Section

This segment explores the concept of buses within computer systems, shedding light on their functionality beyond mere physical connections.

Understanding Computer Buses

- Buses are defined as hardware interfaces responsible for coordinating interactions among various system components rather than just physical wire connections.

- Using keyboards as an example, limitations such as buffer size constraints are discussed alongside their impact on simultaneous keypresses due to storage limitations.

New Section

This part elaborates on how processors handle interruptions efficiently through vector tables and memory management techniques.

Processor Handling of Interruptions

- Processors rely on vector tables stored in memory to determine appropriate handlers based on incoming interruption signals from devices.

- An illustration using keyboard interruptions showcases how processors interpret signals from devices via generated interruptions passed through designated vectors.

New Section

This section delves deeper into processor operations during interruptions by exploring vector tables' significance and their dynamic memory allocation principles.

Dynamic Memory Allocation for Interruption Handling

- Vector tables store pointers directing processors towards relevant interruption handlers based on received signals from devices.

Understanding Interrupt Handling in Computer Systems

In this section, the speaker delves into the process of interrupt handling in computer systems, emphasizing the role of processors and handlers in managing interruptions effectively.

Processor's Role in Interrupt Handling

- The processor switches between processes and changes registers for each process.

- Special handling is done when an interruption occurs to pause the processor.

- Communication with devices like keyboards occurs through memory maps.

Device Interaction and Address Spaces

- There are address gaps related to I/O devices distinct from memory addresses.

- Interrupt handlers manage device configurations and I/O ranges.

Significance of Device Drivers in System Operation

This segment explores the critical role of device drivers in facilitating communication between hardware devices and the operating system.

Device Driver Functionality

- Device drivers handle physical addresses within the system.

- Definition of a driver as a program essential for interacting with physical or virtual devices.

Memory Management and Process Allocation

The discussion shifts towards memory management strategies and process allocation within computer systems.

Memory Organization and Process Allocation

- Operating systems allocate memory uniformly across processes.

New Section

In this section, the speaker discusses the concept of a processor and its connection to devices like light bulbs, emphasizing the role of resistances and voltages in controlling these connections.

Understanding Processors and Connections

- The processor is described as a device that can control its resistance from zero to infinity through a specific line, influencing connected devices like light bulbs.

- The resistance of the processor varies based on voltage levels, with different values corresponding to different states such as 0 or 1.

- Voltage represents the levels associated with different states (e.g., 0 or 1), affecting the flow of current through the processor.

New Section

This segment delves into how voltage levels determine states within processors and their implications for controlling devices.

Voltage Levels and Processor States

- A voltage of 0 or 1 on a pin indicates specific conditions related to grounding and VCC, influencing the behavior of the processor in managing its resistance.

- Processors can act as conductors or non-conductors based on their resistance control capabilities, enabling diverse functionalities in electronic circuits.

New Section

Here, the discussion shifts towards practical applications involving electronic components like switches and buttons controlled by processors.

Electronic Components Control

- Processors can function as electronic switches or buttons programmable through software interfaces, offering versatile outputs for various applications.

Detailed Technical Discussion on Data Transmission and Protocols

In this segment, the speaker delves into the technical aspects of data transmission, focusing on byte beginnings and endings, additional bits for parity control, and the significance of parity control in error-prone communication channels.

Byte Beginnings and Endings

- The speaker discusses the challenge of determining where a byte starts and ends in data transmission.

- Various schemes and tools are used to identify byte beginnings, including parity checks as a primary tool.

Parity Control for Error Detection

- Parity control involves an additional bit to ensure even or odd parity in a data packet, aiding error detection in communication channels prone to errors.

- The use of parity control ensures that the entire packet is consistently either even or odd, facilitating error identification during transmission.

Analog Signals and Device Behavior

This section explores analog signals' behavior in devices like lamps and motors, highlighting their response to varying voltages and resistors for brightness control.

Device Response to Voltage Variations

- Devices such as lamps exhibit different behaviors based on voltage input variations; understanding these responses is crucial for effective device operation.

- Motors respond differently to voltage changes; for instance, a motor may rotate at different speeds based on the applied voltage level.

Brightness Control with Resistors

- By adjusting resistors' values connected to devices like lamps, users can modulate brightness levels effectively.

Generating Analog Signals from Digital Inputs

This part focuses on converting digital inputs into analog signals through pulse width modulation (PWM), enabling the generation of varied output signals from discrete digital inputs.

Pulse Width Modulation (PWM)

- PWM involves varying duty cycles within specific intervals based on digital input levels to generate analog-like signals.

New Section

In this section, the speaker discusses the concept of cleanliness in communication between devices, particularly focusing on UART interfaces.

Understanding Cleanliness in Communication

- The challenge lies in ensuring cleanliness in communication between devices without human intervention. Configuring modems manually can be complex and may require adjustments either physically or programmatically.

- The UART interface consists of five contacts, with a master-slave relationship where the master dictates transmission parameters. Contacts include clock, master out, slave out, and slave select.

- The master generates clock signals for timing and data transmission. It produces a signal similar to a frequency generator's signal. Data bits are transmitted based on these signals between the master and slave devices.

- Through clock signals from the master, corresponding bits are exchanged between devices. This synchronization ensures proper data transmission without ambiguity or errors.

- Master devices manage multiple connected devices by selecting which device to communicate with through specific contact settings. This straightforward protocol is commonly used for efficient communication.

New Section

This section delves into how UART protocols streamline communication by utilizing minimal wiring for effective data exchange.

Simplifying Communication with UART Protocols

- Masters interact with multiple devices and designate the device they wish to communicate with using selection contacts. When set to '1', indicating selection, data transfer occurs specifically with that chosen device.

- UART protocols offer a simple yet widely utilized method for device communication. By requiring only two lines for interaction compared to previous protocols needing three lines, it streamlines connectivity significantly.

- The efficiency of UART protocols is highlighted by their ability to function effectively with just two wires – serial data (TX/RX) and serial clock (CLK). This streamlined approach enhances connectivity while maintaining reliability.

- All devices connect uniformly to these two lines – serial data and serial clock – enabling seamless interaction among various components within a system.

- Each device's capability to independently generate '0' on the wire enhances flexibility in data exchange processes while maintaining simplicity in wiring configurations.

New Section

Exploring the intricacies of initiating and sustaining data transmission through precise timing mechanisms within UART communications.

Timing Mechanisms in Data Transmission

- Initiating data transfer involves setting specific signals such as lowering the clock signal before transmitting actual data bits. This sequential process ensures accurate synchronization during information exchange.

- Master devices control when data transmission begins by manipulating clock signals alongside setting initial bit values before releasing them onto the line for reception by other connected devices.

- Synchronization among connected devices is crucial; delays allow all components to prepare for incoming transmissions effectively before processing new information accurately.

- The simultaneous manipulation of clock signals and data bit values by masters guarantees coherent exchanges during both high (1 state) and low (0 state) periods, optimizing communication efficiency.

Understanding Data Communication Protocols

In this section, the speaker discusses data communication protocols and the intricacies of device interactions in a network.

Device Interactions

- Devices communicate using protocols that dictate how data is transmitted.

- Devices can hold a '0' or '1' until the next clock signal, affecting data flow.

- Clock signals control when data can change, distinguishing between transitional and stable states.

Analog-to-Digital Conversion Process

The speaker delves into analog-to-digital conversion processes and the role of converters in transforming signals for digital processing.

Digital Converters

- Analog and digital converters vary in structure but serve to convert signals effectively.

- Analog-to-digital conversion is crucial for translating analog signals into digital formats for computer processing.

- Understanding how analog-to-digital converters work involves converting physical signals into readable digital values.

Operational Amplifiers in Signal Processing

Operational amplifiers play a vital role in signal processing by comparing input signals to determine output voltages.

Operational Amplifiers

- Operational amplifiers compare two input signals to produce specific output voltages based on their relative values.

- These amplifiers facilitate signal comparison efficiently, aiding in determining which signal is greater or lesser.

New Section

In this section, the speaker discusses the evolution of computer devices and the varying requirements for different types of devices.

Evolution of Computer Devices

- The initial computers had a common design, but it became evident that devices required different specifications, such as high data processing capabilities.

- Devices like video cards are structured with their memory and perform primitive operations quickly. Loading large volumes of data efficiently is crucial for their autonomous operation.

- Different devices have varying data access speeds and interaction patterns, necessitating multiple buses to avoid incorrect associations to a single bus.

New Section

This section delves into the concept of buses in computer architecture and the differentiation based on speed and data access patterns.

Understanding Bus Architecture

- Intel's chipset architecture divided buses into slow and fast categories known as Southbridge (slow) and Northbridge (fast), each connecting various peripherals through controllers.

- Various popular buses like PCIe offer high speed, while USB tends to be slower. The connection buses for disks evolved from older standards like SATA.

New Section

Here, the speaker touches upon the concept of NUMA architecture and uniform memory access in multiprocessor systems.

NUMA Architecture Insights

- NUMA architecture involves multiple processors or cores sharing common memory but facing challenges due to individual cache levels leading to potential issues.

- Cache management becomes critical when processors access shared memory segments independently, requiring protocols like MESI (Modified, Exclusive, Shared, Invalid).

New Section

This part explores cache management challenges arising from processors accessing shared memory segments independently.

Cache Management Challenges

- Processors utilizing cached memory may face discrepancies when one processor modifies a segment while another has an outdated version, leading to protocol innovations like MESI.

- The MESI protocol employs four states - Modified, Exclusive, Shared, Invalid - governing cache line behavior for efficient memory utilization.

New Section

This segment elaborates on cache line states within the MESI protocol for effective cache management strategies.

Cache Line States in MESI Protocol

- The MESI protocol manages cache lines through four distinct states: Modified (can't be modified elsewhere), Exclusive (not shared), Shared (potentially shared), Invalid (outdated).

New Section

The discussion revolves around the concepts of processors, microcontrollers, and their functionalities within devices.

Understanding Processor and Microcontroller Distinctions

- Nodes may be connected for data transmission; various cores like real-time cores can exist within a processor.