Архитектура ЭВМ. Лекция 2: АЛУ. Устройство памяти

Скорость переключения логических схем

Обзор раздела: В этом разделе рассматривается скорость переключения различных логических схем и зависимость этой скорости от количества элементов в схеме.

Скорость переключения логических схем

- Переключение логических схем происходит со своей скоростью, которая зависит от количества элементов в схеме.

- Передача сигнала занимает определенное время, поэтому для управления системой или определения моментов переключения и стабильного состояния требуется использовать синхронизирующий сигнал.

Синхронизация и управление

Обзор раздела: В этом разделе рассматривается необходимость использования синхронизирующего сигнала для управления и контроля переключений в системе.

Использование синхронизирующего сигнала

- Для управления или контроля переключений в системе используется специальный синхрониз

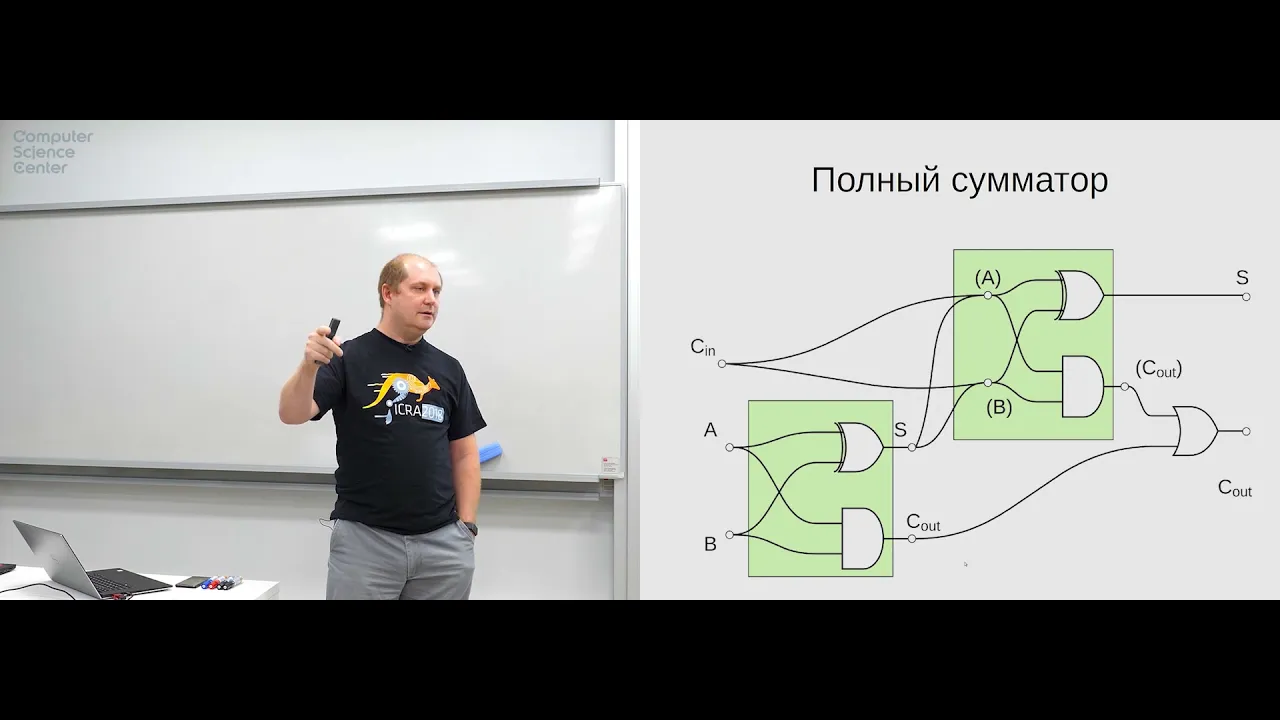

Как создать полу-сумматор

Обзор раздела: В этом разделе рассматривается создание полу-сумматора и его простая структура из логических элементов.

Создание полу-сумматора

- Полу-сумматор можно создать очень просто, используя формулы и логические элементы.

- Для создания полного сумматора необходимо последовательно сложить два бита аргументов и перенос. Результатом будет сумма и новый перенос.

- Если требуется учесть наличие переноса из младшего разряда, можно добавить дополнительный элемент в схему.

- Существуют разные способы обозначения битов чисел в компьютерных системах, например через шины или указанием конкретных битов.

Использование шин для обозначения битов

Обзор раздела: В этом разделе рассматривается использование шин для обозначения битов чисел в компьютерных системах.

Обозначение битов через шины

- Шина - это некоторая линия, на которой передается несколько битов чис

Введение в генерацию и распространение переноса

Обзор раздела: В этом разделе рассматривается концепция генерации и распространения переноса при сложении двоичных чисел.

Генерация и распространение переноса

- Генерация переноса (G): сигнал, который указывает на генерацию переноса при сложении двух битов.

- Распространение переноса (P): сигнал, который указывает на передачу или распространение переноса от младшего разряда к старшему разряду.

- При работе с переносом необходимо учитывать его влияние на результат сложения.

Определение генерации и распространения переноса

- Генерация переноса происходит, когда при сложении двух битов возникает третий бит - перенос.

- Распространение переносят происходит только тогда, когда есть бит переносящего разряда с младшего разряда.

Пример работы генерации и распространения переносят

- При сложении двух чисел, генерация переноса указывает на наличие перенос

Упрощение процесса

Обзор раздела: В этом разделе рассматривается упрощение процесса с помощью использования более крупных блоков и оптимизации времени для получения полной суммы в каждом из этих блоков.

Упрощение процесса

- Можно упростить процесс, чтобы штука скакала более крупными блоками.

- Хочется, чтобы количество времени, которое требуется для получения полной суммы в каждом блоке, соответствовало времени.

- Можно объединить элементы и перенести их туда, где это необходимо, но это может быть дорогостоящей операцией.

Ограничения при создании сложных схем

Обзор раздела: В этом разделе обсуждаются ограничения при создании сложных схем и возможность выбора числа элементов для оптимизации.

Ограничения при создании сложных схем

- Создание сложной схемы, которая выполняет перенос за один такт, может быть дорогостоящей операцией.

- Количество элементов ограничено и зависит от требуемой точности и производительности.

- Необходимо подобрать число элементов таким образ

Блок компараторов

Обзор раздела: В этом разделе рассматривается блок компараторов, который позволяет сравнивать два 8-битных числа и получать различные сигналы на выходе в зависимости от результатов сравнения.

Реализация блока компараторов

- Можно подавать два 8-битных числа на вход блока компараторов.

- Цель - получить различные сигналы на выходе в зависимости от результатов сравнения.

- Используются ассемблерные команды для выполнения операций сравнения (неравенство, равенство, меньше или равно, больше или равно).

Работа блока компараторов

- Если числа равны, на выходе получаем единицу. Если не равны - логическую ноль.

- Если число A больше числа B, на выходе получаем единицу. Если меньше или равно - логическую ноль.

Реализация операций сравнения

- Для определения операции "меньше" используется инвертированный старший бит результата вычитания A и B.

- Для определения операции "больше" используется результат вычитания B из A.

- И

Работа счетчика команд

Обзор раздела: В этом разделе рассматривается работа счетчика команд и его влияние на выполнение программы.

Устройство счетчика команд

- Счетчик команд имеет встроенный счетчик, который указывает номер текущей выполняемой команды.

- Он читает команду и аргументы из памяти, выполняет их и сохраняет результат.

- После выполнения текущей команды переходит к следующей.

Регистры и разрядность чисел

- Регистр - это набор битов памяти, который хранит число определенной разрядности.

- Счетчик хранит n-разрядное число, где n - разрядность числа.

Использование счетчика для управления программой

- С помощью счетчика можно управлять длиной команды и умножать его на длину команды для выполнения операций.

- Счетчик позволяет определить номер текущей выполняемой команды.

Устройство памяти

Обзор раздела: В этом разделе рассматривается устройство памяти и разрядность шин адреса и данных.

Массив памяти

- Память представляет собой массив элементов, которые хранят биты данных.

- Размерность массива определяется разрядностью шины адреса и данных.

Разрядность шин адреса и данных

- Число 2 указывает на 3-битную память, где можно записать 8 чисел.

- Разрядность шины адреса определяет емкость памяти.

Декодеры и многоканальная память

Обзор раздела: В этом раздел

Размещение памяти на чипе процессора

Обзор раздела: В этом разделе рассказывается о размещении памяти на чипе процессора и типах памяти.

Размещение памяти на чипе

- Память размещена на том же чипе, где создан процессор.

- Используется как основной чип, так и подложка для размещения памяти.

Типы памяти

- Оперативная память - отдельное устройство, не связанное с регистрами процессора.

- Динамическая память - использует заряд конденсаторов для хранения информации. Требует постоянного обновления.

- Статическая память - использует триггеры для хранения информации. Более быстрая и стабильная.

Динамическая и статическая память

Обзор раздела: В этом разделе объясняются принципы работы динамической и статической памяти.

Динамическая память

- Хранит информацию в заряде конденсаторов.

- Требует постоянного обновления, так как заряд конденсаторов утекает.

- Используется генератор для постоянного обновления информации.

Статическая память

- Хранит информацию в стабильных ячейках с использованием триггеров.

- Не требует постоянного обновления и проверки состояния.

- Более быстрая и надежная, но занимает больше места на чипе.

Кэш и оперативная память

Обзор раздела: В этом разделе рассказывается о кэше и оперативной памяти.

Кэш

- Кэш - это флип-флоп, который используется в процессоре для временного хранения данных.

- Кэш создается вместе с процессором на одном кристалле.

- Различные типы кэша могут быть использованы для оптимизации работы процессора.

Оперативная память

- Оперативная память - это динамическая память, которая используется для хран